Chelsio Unveils T7 DPU Family to Accelerate Range of Storage, Networking and Security Workloads

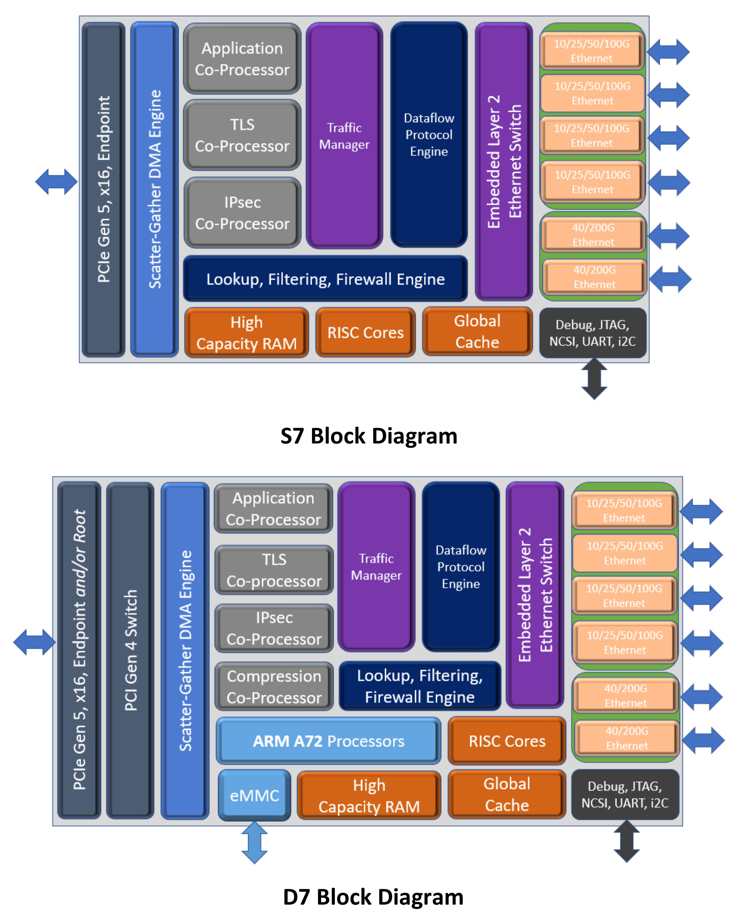

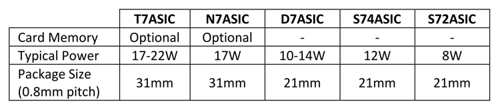

Including T7 ASIC, 31mm package, full suite of features, with optional external memories, S7 ASIC, 21mm package, server offload features without requiring external memories, and D7 ASIC, 21 mm package, full suite of features, without requiring external memories

This is a Press Release edited by StorageNewsletter.com on May 4, 2022 at 2:18 pmChelsio Communications, Inc. introduced its 7th generation Unified Wire DPU product family architected to support and accelerate a range of networking, storage and security workloads supported by enterprise and cloud datacenter applications.

T7 block diagram

The migration to hybrid clouds, multifaceted security requirements, and proliferation of modern applications, such as AI/ML, have accelerated the demand for efficient programmable data-centric processing and storage architectures. By combining performance and low-power compute with 7th generation data-path acceleration, the company’s T7 DPU family provides a ROI benefit through addressing inefficiencies due to overprovisioning of data center compute, networking, and storage resources.

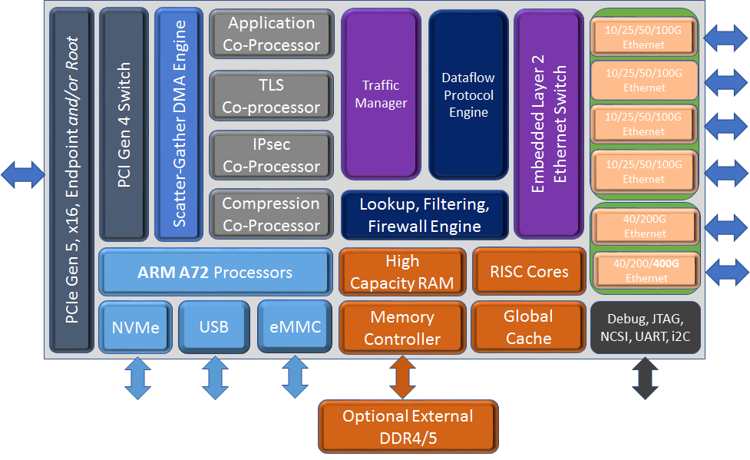

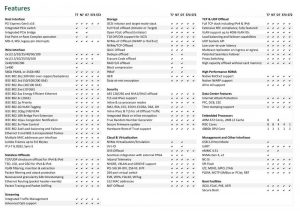

Offering 4x the bandwidth compared to previous generations of Unified Wire, the T7 DPU family incorporates up to 8 Arm Cortex A72 cores for out-of-the-box support of embedded applications for control path processing, seventh generation Very Large Instruction Word (VLIW) processor for storage, networking, and security protocol processing at up to 400Gb,/s using 56Gb PAM4 SerDes. It also integrates PCIe 5.0 x16 with the ability to be either Root Complex and/or End Point, a PCIe switch and an Ethernet switch. The Arm cores are primarily intended for use by the user since the embedded 400Gb/s core and multiple RISC engines will handle the standard protocol processing and offload activities. As such, the T7 DPU provides a higher level of functionality at a lower power dissipation than traditional DPUs that are only based on embedded RISC cores.

T7 DPU supports all the host software of its predecessors, T5 and T6, as-is, thus enabling customers to leverage all prior software investment. It also supports all the features of T5 and T6, and, in addition, adds hardware-based acceleration for RoCEv2, compression, de-dupe, erasure coding, root of trust, as well as a variety of other features. With the single chip iWARP/RoCEv2 implementation that can handle high capacity all-to-all traffic for large clusters, T7 is expected to provide a solid fabric replacement for IB for GPU clusters or HPC installations. The scalability of T7 DPU architecture will continue to meet the upcoming speeds of Ethernet and future generations of Terminator, and thus the portability and preservation of the software investment are both assured.

T7 has evolved the ‘Terminator architecture’ to enable the suite of offloads using the host memory with high capacity while caching a subset of the connections in hardware, and as such removes the need for card memories, thus enabling the single chip server/cloud side instantiations of T7 to run the exact same software as the target/appliance side of the wire with high capacity. The data-flow architecture of the T7 DPU further allows adjusting the clock rates to match the power dissipation to the required workload.

With T7 DPU, the company also enters the computational storage market where on-the-fly compression and encryption increases the effective density of SSD drives. In addition, the native NVMe-NVMe and NVMe-Ethernet bridging function capabilities enable support for a single chip solution to support a suite of storage protocols such as RAID along with the standard networking functions.

T7 further provides a native ability to integrate with FPGAs, and thus provides a flexible platform where an arbitrary task can be decomposed to its parts and run on the offload engines, VLIW engine, FPGA, Arm cores, embedded RISC engines or the host drivers.

“T7 has several confirmed OEM wins already in the cloud, storage, server space, and represents a quantum jump in the level of functionality of our products and provides a generalized solution that can fully address the challenges of efficient data processing and movement across cloud to storage with the confidence of having several generations of offload products in production,” stated Kianoosh Naghshineh, CEO. “T7 ASIC now addresses the Smart NIC, D7 ASIC addresses Computational Storage, and S7 ASIC addresses generic server markets. T7 DPU thus significantly expands Chelsio’s total addressable market and provides a platform and tools to enable Chelsio’s software and solution partners to address several verticals. This collaboration to bring value added products to market together with our software and solution partners is something that we remain very committed to.“

“Robust cutting-edge cloud applications require a new underlying data center infrastructure,” said Greg Schulz, Sr. analyst server, StorageIO. “Chelsio T7 DPU is a new type of I/O processor optimized to process data-centric workloads offloading server CPU overhead of software-defined networking, storage, security and other cloud-native services while boosting application performance.”

T7 DPU models

T7 DPU family is manufactured in TSMC 12FFC process and comprises following models:

T7 DPU family is manufactured in TSMC 12FFC process and comprises following models:

- T7 ASIC, 31mm package, suite of features, with optional external memories

- S7 ASIC, 21mm package, server offload features without requiring external memories

- D7 ASIC, 21 mm package, full suite of features, without requiring external memories

T7 DPU products are undergirded by more than 2 decades of offload products shipped to enterprise customers and by several existing or in progress US patents, such as: 7831745, 7945705, 7616563, 8139482, 8339952, 8155001, 7724658, 7760733, 7715436, 8213427, 7660264, 8686838, 7924840, 7660306, 9537878, 8935406, 589587, 8356112, 8060644, 7826350, 7831720, 8122155, 8856947, 8621627, 9357003, 8886821, 8346919, 8873389, 8806154, 9628370, 9390056, 9413695, 9619245, 9444754, 9684597, 10681145, 9444769, 10225239.

Availability:

- T7 DPU ASICs will be sampling in 3Q22 and similar to T5 and T6, are expected to be in production on first silicon within one quarter of samples.

- T7 DPU emulation platforms for software development are available to early access customers.

- Additional details and samples will be available at the full product launch in 3Q22.

Click to enlarge

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter