Rambus Demos PCIe 5.0 Digital Controller IP

On FPGA platforms

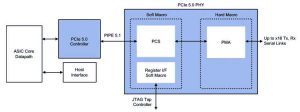

This is a Press Release edited by StorageNewsletter.com on September 10, 2021 at 1:32 pmRambus Inc. has demonstrated its PCIe 5.0 digital controller IP on FPGA platforms.

PCIe 5.0 performance at 32GT/s in FPGAs is using a soft controller. This capability expands the use models of FPGAs by enabling multi-instance, switching and bridging applications and accelerates the performance of FPGAs used in defense, networking, and test and measurement markets.

“We’ve achieved a new industry benchmark with the demonstration our PCIe 5.0 controller operating at 32 GT/s on popular FPGA platforms,” said Scott Houghton, GM, interface IP. “With the growing importance of FPGAs in markets from defense to the data center, this solution developed by the newly-acquired PLDA team expands the Rambus portfolio and offers the next level of performance for mission-critical applications.“

Features of Rambus PCIe 5.0 digital controller:

-

Verified on leading FPGA platforms

-

Supports up to 32GT/s data rates

-

Backwards compatible to PCIe 4.0 and 3.1/3.0

-

Supports Endpoint, Root-port, Dual-mode, and Switch-port configurations

-

Supports up to 64 Physical Functions (PF), 512 Virtual Functions (VF)

-

Supports AER, ECRC, ECC, MSI, MSI-X, multi-function, crosslink, DOE, CMA over DOE, and other optional features and ECNs

Resources:

Rambus digital controller

Rambus interface IP, including PHYs and controllers

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter