Astera Labs: Availability of Aries Smart Retimers for PCIe 4.0 and 5.0 Interconnects

And launches Cloud-Scale Interop Lab.

This is a Press Release edited by StorageNewsletter.com on August 21, 2020 at 2:27 pmAstera Labs, Inc. announced that its Aries Smart Retimers designed to PCIe 4.0 architecture (PT4161L) have entered mass production while Aries Smart Retimers designed to PCIe 5.0 architecture (PT5161L) are being sampled with strategic customers.

“Production release of PT4161L x16 PCIe 4.0 Smart Retimers and active sampling of pin-compatible PT5161L x16 PCIe 5.0 Smart Retimers is a critical milestone for the industry, clearing the way for wide deployment of PCIe solutions,” said Jitendra Mohan, CEO. “Alongside our products, we are unveiling our Cloud-Scale Interop Lab service which provides the necessary testing infrastructure to our customers to ensure seamless interoperation and robust designs of their PCIe 4.0 and PCIe 5.0 systems.“

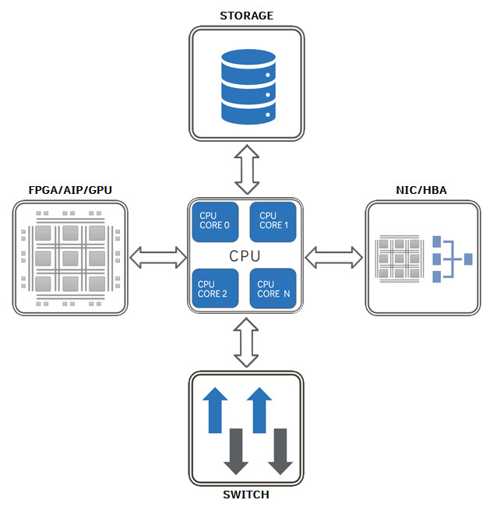

Aries Smart Retimers is a pin compatible PCIe 4.0 and 5.0 retimer upgrade solution with deployment at multiple cloud and server OEMs, and interoperability testing alongside leading CPU, GPU and end point vendors.

“QCT understands that higher-bandwidth, lower-latency PCIe 5.0 and 4.0 interconnects are essential for cloud-optimized solutions to run specialized workloads, such as AI and ML,” said Mike Yang, president, Quanta Cloud Technology (QCT), company’s parent of Quanta Computer, Inc. “QCT is leading the way to solve these next-gen datacenter design and operation challenges, and we are excited to partner with Astera Labs on purpose-built PCIe Smart Retimer solutions.“

“We are pleased to collaborate with Astera Labs using our industry-leading manufacturing techniques to deliver Aries Smart Retimers to market,” said Bradford Paulsen, SVP, business management, TSMC North America. “We look forward to quickly satisfying the massive customer demand for their cloud-optimized connectivity solutions.“

“PCIe 5.0 technology is critical to the next-gen device interconnect and acceleration of heterogenous compute architectures,” said Michael Hall, director, technology and ecosystem enabling, Intel Corp. “Enterprise PCIe 40 and 5.0 retimer solutions that interoperate with Intel platforms, such as Astera Labs’ Aries Smart Retimers, are instrumental to the enablement of high-performance standard PCIe 5.0 interconnect across the entire ecosystem.“

“As a PCI-SIG member, Astera Labs has been a contributor to the advancement of our specs with its expertise of PCIe retimer technology,” said Al Yanes, chairman and president, PCI-SIG. “It is great to see Aries Smart Retimers broadly available to system developers, which will enable rapid PCIe 4.0 technology and PCIe 5.0 technology ecosystem expansion.“

Unveils Cloud-Scale Interop Lab with Ecosystem partners

The company has launched its Cloud-Scale Interop Lab as an ongoing collaboration with industry partners, so customers can design, reduce development time and trust that integration of Aries Smart Retimers will be straightforward.

“Samsung is driving storage performance boundaries with its PCIe 4.0 PM1733 and PM1735 SSD solutions, which deliver cutting-edge memory capabilities to address today’s enterprise data demands,” said Hangu Sohn, VP, NAND memory planning, Samsung Electronics. “The Cloud-Scale Interop Lab from Astera Labs helps ensure seamless interoperability within the latest PCIe 4.0 systems and verifies that the resulting connection can handle the rigors of enterprise operation.”

“PCIe 4.0 technology can help remove storage performance bottlenecks for next-gen data center applications and use cases, and we’re excited to take part in Astera Labs’ Cloud-Scale Interop Lab to support Aries Smart Retimers for enterprise PCIe 4.0 system designers,” said Richard New, VP, research, Western Digital Corp.

Resources:

Video: Cloud-Scale Interop Lab – How We Test

Video: Interop Bulletin #1: Interop Testing for Popular Endpoints

Video: Interop Bulletin #2: Interop Testing for Enterprise NVMe SSD Deployments

Aries Smart Retimers Interop Report (registration required)

Read also:

Astera Labs: Smart Retimer Portfolio for PCIe 4.0 and 5.0 Solutions

For workload optimized platforms to support new server backbones that are high-bandwidth with low latency

October 31, 2019 | Press Release

PCI-SIG DevCon Taiwan: Astera Labs Demos PCIe 5.0 System Deployment in Collaboration With Intel and Synopsys

With Smart Retimer 32GT/s retimer SoC designed to PCIe 5.0 spec, doubles signal reach and achieves plug-and-play interoperation without compromising interconnect topologies even at 32 GT/s speeds.

October 28, 2019 | Press Release

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter