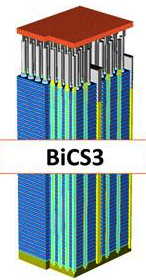

512Gb Three-Bits-per-Cell 64-Layer 3D NAND BICS3 Chip by Western Digital and Toshiba

Mass production expected in second half of 2017

This is a Press Release edited by StorageNewsletter.com on February 17, 2017 at 2:08 pmWestern Digital Corp. (WDC) announced that it has commenced pilot production of the company’s 512Gb three-bits-per-cell (X3) 64-layer 3D NAND (BICS3) chip in Yokkaichi, Japan, with mass production expected in the second half of 2017.

“The launch of the industry’s first 512Gb 64-layer 3D NAND chip is another important stride forward in the advancement of our 3D NAND technology, doubling the density from when we introduced the world’s first 64-layer architecture in July 2016,” said Dr. Siva Sivaram, EVP, memory technology, Western Digital. “This is a great addition to our rapidly broadening 3D NAND technology portfolio. It positions us well to continue addressing the increasing demand for storage due to rapid data growth across a wide range of customer retail, mobile and data center applications.“

The 512Gb 64-layer chip was developed jointly with the company’s technology and manufacturing partner Toshiba Corporation. WDC first introduced initial capacities of the world’s first 64-layer 3D NAND technology in July 2016 and the first 48-layer 3D NAND technology in 2015; product shipments with both technologies continue to retail and OEM customers.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter