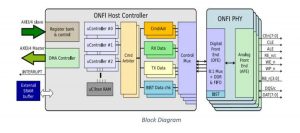

Arasan Chip Systems ONFI v5.0 Compliant NAND Flash IP With Host Controller IP, PHY IP and Software Stack

ONFI 5.0 standard 50% faster than ONFI 4.2

This is a Press Release edited by StorageNewsletter.com on August 13, 2021 at 1:01 pmArasan Chip Systems, Inc., provider of semiconductor IP for IoT, mobile and automobile SoCs, announces the availability of their total IP solution for NAND flash compliant to the Open Nand Flash Interface (ONFI) 5.0 spec.

Arasan Onfi 5.1 Controller IP

Click to enlarge

The company’s Total IP for ONFI v5.0 NAND flash includes the Host Controller IP, PHY IP and software stack. The ONFI 5.0 standard is 50% faster than the previous ONFI 4.2 standard. ONFI Test Chip is available on 12nm.

This NAND Flash Controller IP enables simple, dependable access to off-chip NAND flash devices at previously unheard-of speeds. The updated controller supports all ONFI spec modes at all speeds.

This includes the NV-LPDDR4 mode, in addition to the legacy Single Data Rate (asynchronous), NV-DDR (synchronous), NV-DDR2, and NV-DDR3 double data rate modes. It supports all timing modes for these interface modes, from the low 10MHz mode up to the brand new 1,200MHz (2.4GT/S) I/O speeds. The firm’s ONFI 5.0 Host controller IP is the first in the company’s ONFI host controller line to have a fully verified AXI interface. It comprises microcontroller architecture, to make sure every ONFI data path is fully utilized in a multithreaded fashion. The firm’s ONFI 5.0 Host controller IP also features a full Scatter gather Direct Memory Access (DMA) algorithm, capable of moving from the flash to system memory at speeds matching the speed of the flash interface.

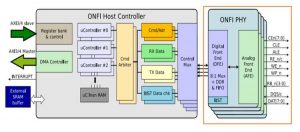

Arasan Onfi 5.1 Phy IP Scheme

Click to enlarge

The firm’s ONFI 5.0 PHY IP is designed to connect with their ONFI 5.0 Host Controller IP. This ONFI 5.0 PHY has complete SDR, NV-DDR, NV-DDR2, NV-DDR3 and NV-LPDDR4 TX/RX functionality and supports all the speeds defined in the ONFI spec while remaining backwards compatible with the prior versions of the ONFI specs. The ONFI 5.0 PHY enables data training, various power drives and ZQ calibration, which ensures operating speed and optimum signal integrity. The PHY uses a PLL/DLL combination to provide flexible frequency access. The PHY also includes ESD protection on all of the various ONFI interface pins.

The ONFI 5.0 NAND Flash Controller IP and PHY are available to license. The PHY is available on nodes 12nm and below.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter