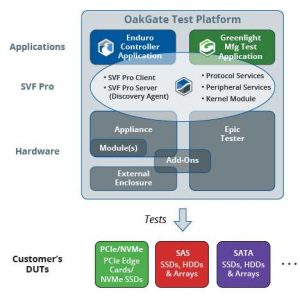

OakGate: Availability of Memory Fencing Technology for Storage Test Platform

Test and validation platforms to detect errors that occur when SSD accesses memory locations outside area specified by device driver

This is a Press Release edited by StorageNewsletter.com on April 12, 2019 at 2:15 pmOakGate Technology, Inc. announces a patent-pending memory fencing technology.

By incorporating memory fencing technology to its already storage test platform, the company is pushing the boundaries to provide a critical error detection tool for its customers. Prior to that, users could not set memory address ranges (memory fences or barriers) for the purpose of error detection or security in either test or production environments.

“The OakGate team has a rich heritage of pioneering key storage I/O technologies that later became the de-facto industry standards. We are continuing this tradition with our innovative memory fencing technology,” stated Bob Weisickle, co-founder and CTO, OakGate. “With this patent-pending technology, we are now able to offer customers a valuable tool to detect errors caused by illegal memory access.”

The memory fencing capability is enabled by this patent-pending method of mapping physical memory locations through the I/O memory management unit (IOMMU) to a set of virtual addresses for specific devices on the PCIe backplane. Currently in a test system used to test direct memory access (DMA) devices, the available address range is limited to a numerical range associated with the size of the physical memory. This limitation does not allow the test system to validate memory access beyond that limited range. The firm’s DMA mapping technology enables the test system to fence, detect, and authenticate memory access throughout the full DMA address range.

The company’s memory fencing technology has been incorporated in the firm’s fourth generation SVF software suite, Enduro/SVF Pro v4.2. By selecting this option within Enduro (the user interface), the user can check all memory accessed by the device under test (DUT) to the range which has been specified for that device. If the DUT attempts a memory access outside the specified range, the software flags the operation as an error. It detects and categorizes these errors, and provides the address and operations of the DUT that is violating the memory access.

Key benefits of memory fencing technology are two-fold:

-

In a test or development environment, it detects the errors that occurred when a DUT accesses memory space outside of the area specified for the device. These errors range from data corruption to total system failure. Normally, these errors can be difficult and time consuming to debug, but with this technology, these errors can be caught early in the development process, averting more complex issues that are nearly impossible to root cause.

-

In the field, it detects when a device purposely accessed memory outside the specified range – preventing system hacking, unauthorized data access, and/or infecting a system with a virus.

The memory fencing technology is available with Enduro/SVF Pro v4.2 and later.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter