Start-Up Rangduru in Non-Volatile Memory for Logic Process

In discrete and also embedded forms for SSDs

By Jean Jacques Maleval | August 11, 2015 at 3:27 pmRangduru, Inc. is a privately-held fabless start-up based in San Jose, CA, and founded in February 2011 by its CEO Euipil Kwon.

Kwon was formerly senior design engineer at MoSys since 2006, designing bandwidth engine and 1T SRAM macros, and previously at O2IC, T-RAM and Samsung Electronics.

Kwon was formerly senior design engineer at MoSys since 2006, designing bandwidth engine and 1T SRAM macros, and previously at O2IC, T-RAM and Samsung Electronics.

The company has been funded by business angels but didn’t get financial funding from VCs up to now.

It designs and develops low-cost, high density non-volatile memory (NVM) technology for embedded use in a range of micro-controllers, ASICs and related semiconductor products.

The embedded solution is aimed at system-chips set-top boxes, microcontrollers, and DSPs, at memory capacities of up to 256Mb, and the standalone memory for one-time programmable (OTP) cards, USB memory and SSDs.

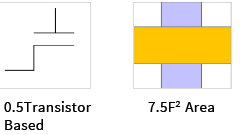

Rangduru’s DX OTP Macro is a field programmable NVM macro using 0.5T bit cell technology, which is smaller than the conventional technology like 1T/2T bit cell.

The half transistor (0.5T) bit cell technology provides better bit cost, higher reliability and lower overall product cost than NOR flash.

The DX OTP provides this reduced cost and increased density through the ability to use standard semiconductor logic processes, with just one extra mask. This avoids the costly use of non-standard processes.

Additionally, it enables large capacity on-chip NVM solution for MCUs/SoCs, hence opening new high density on-chip NVM applications requiring high speed, low power consumption, high security, space reduction, and low cost in total system.

DX OTP Features

- Bit cell structure: 0.5 Transistor based

- Bit cell size: 7.5F2

- Bit cell process: Standard CMOS Logic Process plus one extra mask

- On-chip capacity: Up to 256Mb beyond 4Mb Scalable to 20nm node and below

The company assigned a US patent number 9,087,588 from its CEO in July 21, 2015, Programmable non-volatile memory.

Abstract: A programmable non-volatile memory including a memory cell includes a transistor acting as an anti-fuse and two diodes for access. The memory cell that can store two bits and includes a transistor acting as an anti-fuse and two diodes for access, wherein the cell transistor includes: the source electrode formed by a metal, the first diode as the source region contact structure, the drain electrode formed by a metal, and the second diode as the drain region contact structure wherein the cell transistor, the oxide layer between the source area and the gate is the first anti-fuse the first storage, the oxide layer between the drain area and the gate is the second anti-fuse the second storage, the two diodes are connected in series to access the two anti-fuses.

Subscribe to our free daily newsletter

Subscribe to our free daily newsletter